CS 208 s21 — Learning Block #19

Table of Contents

1 Warmup

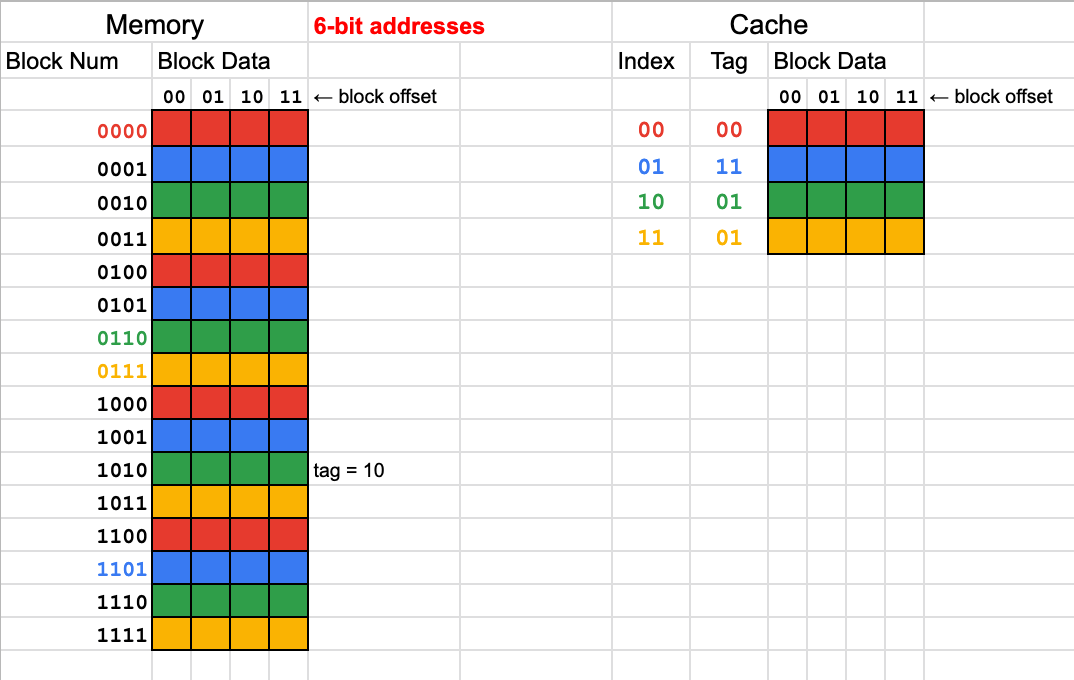

1.1 Conflict

- what happens if we access these two addresses in alternation?

- every access is a cache miss, replacing the address that was just loaded in on the last miss

- rest of the cache goes unused

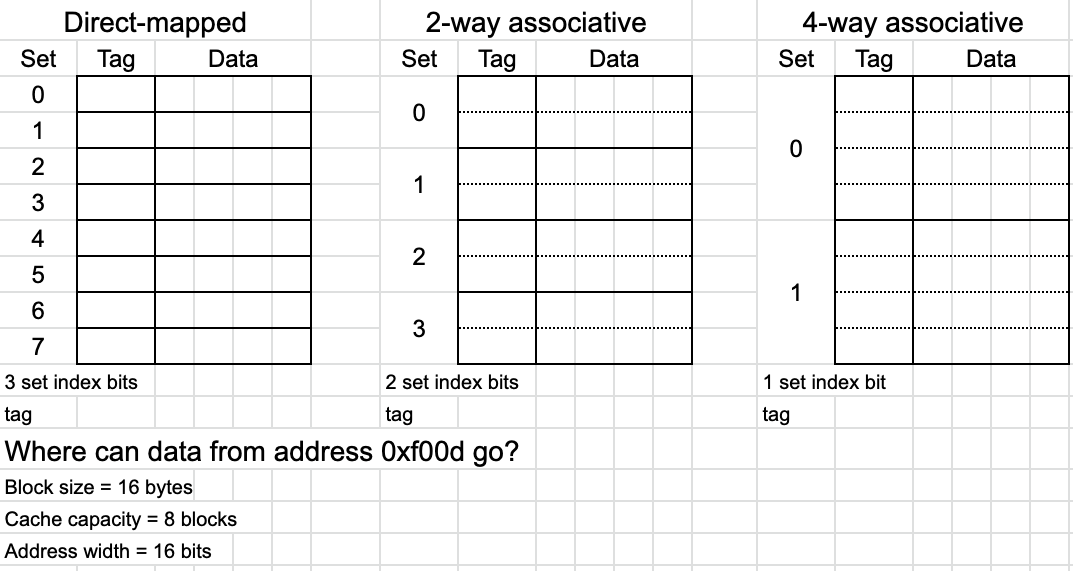

2 Associativity Exercise

| block size | capacity | address width |

|---|---|---|

| 16 bytes | 8 blocks | 16 bits |

In what sets could data from address 0xf00d be placed in a direct-mapped, 2-way associative, and 4-way associative cache with the above properties?2

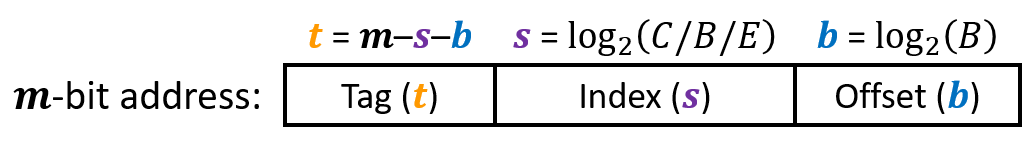

3 Cache Parameter Exercise

With 12-bit addresses, a 256 byte cache, 32 byte block size, and 2-way associativity, how are addresses used for caching?3

4 Practice

CSPP practice problems 6.12–6.16 (p. 628–630) will be a good warmup for implementing lab 4

Footnotes:

1

0x0a and 0x28, both have set index bits 10

2

See exercise on the spreadsheet.

3

32-byte block size means 5 block offset bits. \(C = 256\), \(B = 32\) and \(E = 2\) (2-way associative), so \(S = C / B / E = 4\). \(s = \log_2 S = 2\) set index bits. That leaves \(12 - 5 - 2 = 5\) tag bits.